## Spezifikation

Power Off By Program – Herunterfahren des NKC mit einem ATX-Netzteil per Programm

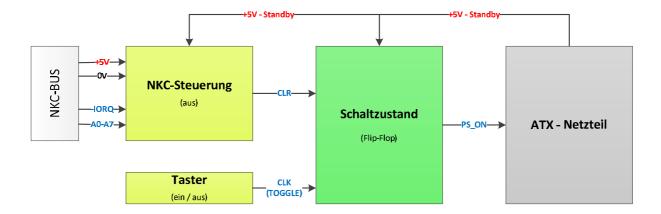

NKC-BUS

NKC-Steuerung

(Flip-Flop)

Schalt-

zustand

ATX -Netzteil

sEn

Taster (ein / aus)

#### Version 1.0

Idee:

Sascha Neuschl Pirolweg 21 48167 Münster

Email: scn69@gmx.de

#### **Dokumentenhistorie**

| Version | Autor(en)       | Änderung      | Datum      |

|---------|-----------------|---------------|------------|

| 1.0     | Neuschl, Sascha | Erste Version | 07.09.2020 |

|         |                 |               |            |

|         |                 |               |            |

|         |                 |               |            |

|         |                 |               |            |

## Inhaltsverzeichnis

| 1 | Vor  | wort                   | . 4 |

|---|------|------------------------|-----|

|   | 1.1  | ldee                   | . 4 |

|   | 1.2  | Ansatz                 | 4   |

|   | 1.3  | Aktueller Stand        | 4   |

| 2 | Bes  | chreibung des Konzepts | 4   |

|   | 2.1  | Konzept                | 4   |

|   | 2.2  | Besonderheiten         | 5   |

| 3 | Sch  | altplan                | 6   |

| 4 | Pro  | gramm                  | 7   |

| 5 | Stüd | ckliste                | 7   |

| 6 | Anh  | ang                    | 8   |

|   | 6.1  | 74LS73                 | 8   |

|   | 6.2  | 74LS132                | 8   |

|   | 6.3  | 74LS688                | g   |

#### 1 Vorwort

#### **1.1 Idee**

Da man ja praktisch nie einen PC mit dem Einschaltknopf wieder ausschaltet, sondern per Menü mit einem Programm, wollte ich das auch für meinen NKC haben.

#### 1.2 Ansatz

Bei dem als Spannungsversorgung eingesetzten ATX-Netzteil sollte die "**PS\_ON" – Leitung** per Taster und Programm mit einer kleinen Karte gesteuert werden.

#### 1.3 Aktueller Stand

Es gibt eine auf Lochrasterplatine aufgebaute und funktionierende Schaltung.

## 2 Beschreibung des Konzepts

#### 2.1 Konzept

Wenn die "PS\_ON" – Leitung eines ATX-Netzteils mit 0 Volt verbunden wird, dann startet es. Wird diese Verbindung getrennt, stoppt es. Dies wird beim NKC i.d.R. durch einen einfachen Schalter erreicht.

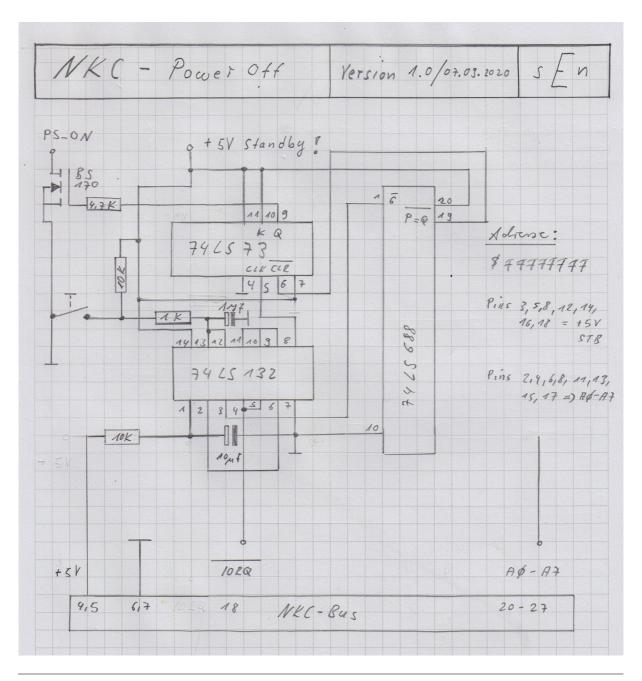

- Der Schalter wird hier durch einen FET BS170 ersetzt.

- Der FET wird durch den Q-Ausgang eines Flip-Flops 74LS73 angesteuert.

- Der Zustand des Flip-Flops wird geändert ...

- o durch einen Taster, der auf dem CLK-Eingang einen Übergang 1-0-1 erzeugt:

- J und K des Flip-Flops liegen auf +5 Volt, sodass es mit dem Takt toggelt.

- Damit kann durch Drücken des Tasters der Q-Ausgang auf 1 bzw. 0 geschaltet werden.

- Das Netzteil kann also ein- und ausgeschaltet werden.

- o Durch **Ansteuerung des -CLR-Eingangs** (RESET) aufgrund eines Signals:

- Ich tue das mit dem Signal "-P=Q" eines Adressdecoders 74LS688 auf der IO-Adresse \$FFFFFFFF.

- Genauso gut könnte man eine IO-Port verwenden.

- Der Q-Ausgang geht dann taktunabhängig auf 0.

- Das Netzteil kann also nur ausgeschaltet werden.

#### 2.2 Besonderheiten

Damit die Schaltung am Ende zuverlässig funktioniert, sind einige Besonderheiten zu beachten:

- Die Schaltung muss **immer mit einer Versorgungspannung bedient** werden. Deshalb wird die **Standby-Leitung des ATX-Netzteils** verwendet.

- Der Taster muss entprellt werden, da sonst nicht nur ein sondern unter Umständen mehrere Taktzyklen ausgelöst werden. Die geschieht durch ein Tiefpassfilter gefolgt von einem Schmitt-Trigger. Als Schmitt-Trigger werden 2 NAND-Gatter eines 74LS132 eingesetzt, weil an anderer Stelle die NAND-Funktionalität benötigt wird.

- Es muss verhindert werden, dass beim Einschaltvorgang des Computers über den Taster auf dem NKC-Bus die Signalkombination "-IORQ = 0 und "A0-A7 = \$FF" entsteht. Denn sonst wird das Netzteil gleich wieder ausgeschaltet, weil "-CLR" des Flip-Flops über den Adressdecoder ausgelöst wird:

- Es reicht an dieser Stelle, das Signal "- IORQ" für eine bestimmte Zeit nicht auszuwerten, bis stabile Verhältnisse auf dem NKC-Bus herrschen. Man kann sich dabei auch "Zeit lassen", weil man i.d.R. den Computer nach dem Einschalten nicht gleich wieder ausschalten möchte.

- Das "-IORQ" Signal wird mit einem NAND-Gatter des 74LS132 invertiert und auf den 1. Eingang eines weiteren NAND-Gatters geschaltet.

- Auf den 2. Eingang wird ein Kondensator gegen 0 Volt und 1 Widerstand gegen

+5 Volt des NKC-Busses geschaltet.

- Idee ist, dass wenn das Netzteil eingeschaltet wird, erst dann die +5 Volt auf dem NKC-Bus anliegen. Und solange der Kondensator nicht ausreichend geladen ist, verhindert er das Durchschalten des 2. NAND-Gatters. Damit kann auch bei aktiviertem "-IORQ" – Signal der Eingang "-G" des Adressdecoders nicht freigegeben werden.

Spezifikation Stand: 20.02.2020 Seite 5 von 9

## 3 Schaltplan

Spezifikation Stand: 20.02.2020 Seite 6 von 9

## 4 Programm

Wenn die Schaltung aufgebaut und angeschlossen ist, kann man mit dem Taster das Netzteil ein- und ausschalten.

Ist das Netzteil eingeschaltet, kann es nun mit einem ganz einfachen Programm ausgeschaltet werden, denn es muss nur die Adresse auf den Bus gelegt werden, die am Adressdecoder eingestellt ist. In meinem Fall ist das die IO-Adresse \$FFFFFFF in einem 68008-System.

#### Dafür lautet das Programm dann einfach:

# start: move.b \$FFFFFFF, d0 rts

Dann kann man das einfach assemblieren als z.B. **"end.68k" in JADOS**. Und fortan kann man den NKC mit "end" ausschalten.

### 5 Stückliste

| Spezifikation                          | Stand: 20.02.2020                             | Seite 7 von |

|----------------------------------------|-----------------------------------------------|-------------|

| 10 ΚΩ                                  |                                               | 2 Stück     |

| 4,7 ΚΩ                                 |                                               | 1 Stück     |

| 1,0 ΚΩ                                 |                                               | 1 Stück     |

| Widerstände:                           |                                               |             |

| Taster – einmal "ein"                  |                                               | 1 Stück     |

| IC-Fassung – 10 polig                  |                                               | 1 Stück     |

| IC-Fassung – 7-polig                   |                                               | 2 Stück     |

| Gerade Stiftleiste – 2 reihig, 8 polig |                                               | 1 Stück     |

| Gewinkelte Stiftleiste – 4 polig (+5 V | STB und PS_ON vom Netzteil / Tasteranschluss) | 1 Stück     |

| Gewinkelte Stiftleiste – 27 polig (NKO | C-Bus)                                        | 1 Stück     |

| Lochrasterplatine                      |                                               | 1 Stück     |

#### Kondensatoren:

| 100 nF           | 3 Stück |

|------------------|---------|

| 1,0 µF / 35 Volt | 1 Stück |

| 10 μF / 35 Volt  | 1 Stück |

ICs:

| 74LS73  | 1 Stück |

|---------|---------|

| 74LS132 | 1 Stück |

| 74LS688 | 1 Stück |

## 6 Anhang

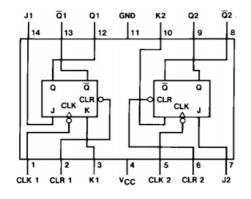

#### 6.1 74LS73

#### **Connection Diagram**

#### **Function Table**

|     | Inputs |   |   | Out   | puts             |

|-----|--------|---|---|-------|------------------|

| CLR | CLK    | J | K | Q     | Q                |

| L   | X      | X | X | L     | Н                |

| н   | 1      | L | L | $Q_0$ | $\overline{Q}_0$ |

| н   | ↓      | н | L | Н     | L                |

| н   | ↓      | L | Н | L     | Н                |

| н   | 1      | Н | Н | Tog   | ggle             |

| н   | н      | X | X | $Q_0$ | $\overline{Q}_0$ |

- H = HIGH Logic Level

- L = LOW Logic Level

- X = Either LOW or HIGH Logic Level

- $\downarrow$  = Negative going edge of pulse.  $Q_0$  = The output logic level before the indicated input conditions were

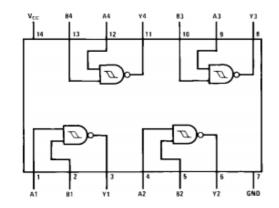

#### 6.2 74LS132

#### **Connection Diagram**

#### **Function Table**

| Y | = | A | В |  |

|---|---|---|---|--|

|   |   |   |   |  |

| Inp | Inputs |   |

|-----|--------|---|

| A   | В      | Y |

| L   | L      | Н |

| L   | Н      | н |

| н   | L      | н |

| н   | Н      | L |

H = HIGH Logic Level L = LOW Logic Level

Seite 8 von 9 Spezifikation Stand: 20.02.2020

Toggle = Each output changes to the complement of its previous level on each falling edge of the clock pulse.

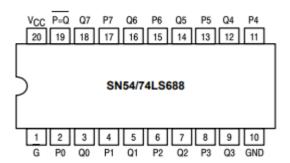

#### 6.3 74LS688